ARM 아키텍처 배경지식 (ARMv8)

[ 목 차 ]

1. ARM Arcitecture 소개

- 스마트폰을 비롯한 대부분의 모바일 기기에서 사용되는 저전력 chip의 대표적인 아키텍처

- 실제로 ARM 프로세서는 현재 국제 시장에서 1,600억 개 이상 출하되었으며 IoT, 스마트폰을 비롯한 다양한 분야에서 폭넓게 사용되고 있다.

- ARM Architecture는 대표적인 RISC 계열의 마이크로프로세서로 구조가 단순하고 소비전력이 낮으면서 고성능이라는 특징을 가지고 있다.

- 따라서 Intel 프로세서와 ARM 프로세서에는 많은 차이점이 있지만 가장 큰 차이점은 명령어 세트이다. 인텔은 CISC (Complex Instruction Set Computing) 프로세서로서 더 크고 기능이 풍부한 명령어 세트를 가지고 있으며 많은 복잡한 명령어가 메모리에 접근 할 수 있도록 하여 처리하는 작업이 많지만, ARM 프로세서보다 레지스터가 적다.

A. ARMv8 Architecture

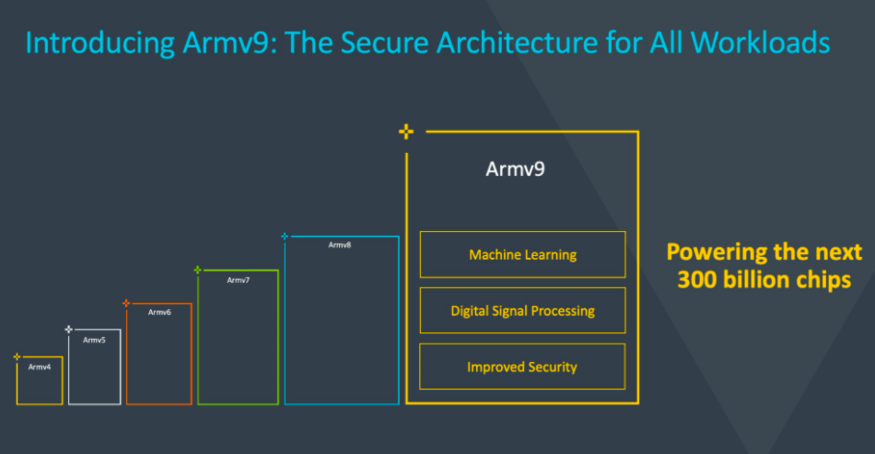

- ARM 아키텍처는 [그림 1]과 같이 발전하였으며 최근에는 ARM holdings에서 차세대 아키텍처인 ARMv9을 공개하였다.

- 현재 스마트폰과 같은 대부분의 모바일 기기에서 ARMv8 기반의 칩을 사용하고 있으며 Apple에서 ARM 기반의 M1 chip을 탑재한 맥북(MacBook)과 아이맥(iMac) 출시하면서 앞으로 모바일 기기 뿐만 아니라 더 많은 기기에서 사용할 것으로 보인다[3].

- 애플뿐만 아니라 마이크로소프트와 엔디비아 역시 ARM 기반의 칩을 사용 자체적인 프로세서 개발을 진행 중에 있다[4,5].

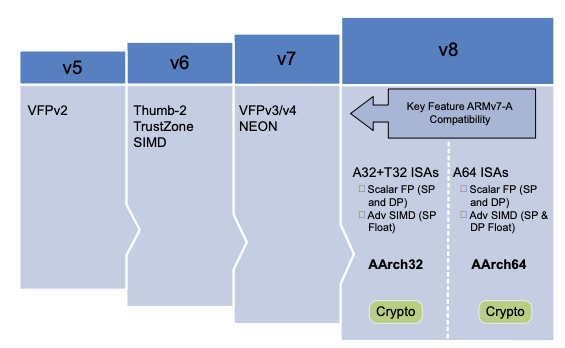

- ARMv8 아키텍처는 ARMv7과 비교하였을 때 64비트 아키텍처라는 특징이 있다. 하지만 실행상태라는 개념을 도입하여 [그림 2]와 같이 AArch64라는 64비트 실행상태와 AArch32라는 32비트 실행상태를 포함하고 있으며 32비트용 ARMv7 소프트웨어와의 하위 호환성을 유지한다.

- AArch64는 64비트의 실행상태를 사용하므로 성능적으로 이점이 존재한다[2,6,7].

- 물리 주소의 범위가 확장되어 프로세서가 4GB 이상의 주소에 접근 가능하다.

- 공유 라이브러리 및 실행 파일 내에서 효율적인 데이터 주소 지정을 위해 PC(Program Counter) 주소+/- 4GB로 커졌다.

- 4GB 이상의 가상 메모리를 사용할 수 있다.

- 하드웨어 암호화 명령어의 지원으로 암호화 및 복호화 성능이 향상하였다

B. ARM Exception

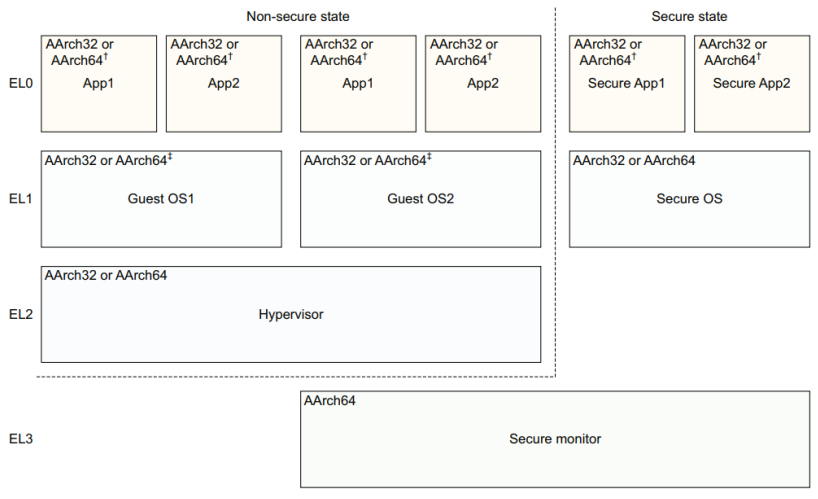

- ARMv8에서는 [그림 3]과 같이 EL0, EL1, EL2, EL3 까지의 Exception level을 정의

- Exception은 시스템 흐름에서 벗어나 Exception Handler 처리가 필요한 상태 또는 시스템 이벤트를 말함.

- Exception level 중 EL0에서의 실행은 권한 없는 실행, EL1은 권한 실행이라고 하고 EL2는 하이퍼바이저가 동작하며 EL3은 Secure monitor로 ARM TrustZone 기술을 사용하는 기기에서만 존재한다.

- Secure monitor와 ARM TrustZone에 관한 내용은 따로 포스팅할 예정

- 만일 Exception이 발생하면 같은 Exception level이나 높은 Exception level로 이동하게 되는데 만약에 EL0에서 EL1로 Exception level이 변경된다면 소프트웨어의 실행 권한도 상승한다.

- 따라서 의도하지 않은 권한 상승이 발생하면 문제가 발생할 수 있으므로 발생한 Exception level보다 낮은 level에서는 Exception handling이 불가능하다. Exception이 발생하는 상황은 다음과 같다[6][7].

- IRQ와 FIQ Interrupt Signal

- 메모리 시스템 Abort

- System Call

- Undefined Instruction 실행

- Secure monitor나 하이퍼바이저 Trap

2. ARMv8 레지스터

ARMv8 아키텍처에서는 특수목적 레지스터, 시스템 레지스터, 범용 레지스터 (General-purpose Register, GPR), SIMD & FP(SIMD & Floating-Point register), 시스템 컨트롤 레지스터(SCTLR) 등이 존재한다[2].

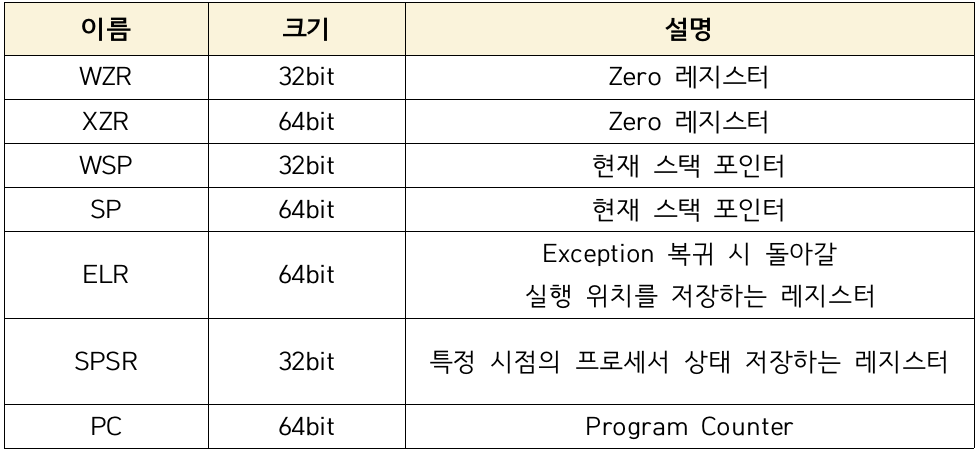

A. AArch64 특수목적 레지스터

AArch64의 특수목적 레지스터는 [표 1] 과 같으며 WZR, XZR의 경우 각각 32비트, 64 비트에서 사용되는 Zero 레지스터를 의미한다. 이 때 Zero 레지스터는 모두 0으로 읽히며 목적 레지스터로 사용할 때는 무시된다.

SP, WSP는 스택의 현재 위치를 가리키는 레지스터로 Exception Level에 따라 SP_ELn으로 사용한다. ELR 레지스터는 Exception Link 레지스터로 Exception Level에 따라 ELR_ELn(복귀할 Exception Level이 없는 EL0 는 제외)으로 사용하고 Exception 복귀 시 돌아갈 return address를 저장하고 있다.

SPSR 레지스터(Saved Process Status Register)는 ARMv7의 CPSR과 유사한 방식으로 Exception이 발생하면 PSTATE로부터 SPSR 레지스터에 저장된다. Exception을 발생시킬 수 없는 EL0를 제외한 Exception Level 마다 존재하며 SPSR_ELn으로 사용한다.

PC(Program Counter) 레지스터는 다음에 실행할 명령어의 위치를 저장하는 레지스터로 ARMv7과 달리 프로그래머가 ARMv8에서는 접근하여 수정하는 것은 불가능하다[2,6].

B. AArch64 PSTATE

AArch64에는 ARMv7에서의 CPSR(현재 프로세스 상태 레지스터)와 동일한 기능을 가진 레지스터가 없다.

AArch64에서 기존 CPSR의 구성요소는 독립적인 field로 제공되며 이를 프로세서 상태(PSTATE)라고 한다. PSTATE field는 아래 [표 2]와 같다.

AArch64에서는 ERET 명령어를 수행하여 Exception 발생 시 PSTATE가 갱신되고 몇몇 비트가 SPSR_ELn에 복사된다. 그리고 Exception으로부터 복귀할 때에는 SPSR_ELn가 PSTATE로 복사된다. PSTATE 필드 중 N, Z, C, V 필드는 EL0에서 접근할 수 있지만 다른 모든 PSTATE 필드는 EL1 이상에서 실행될 수 있고 EL0에서는 정의되지 않는다[5].

C. AArch64 범용 레지스터

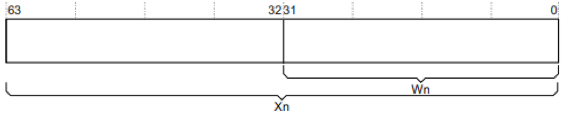

AArch64 실행상태에서는 64비트의 범용 레지스터인 X0~X30을 가지고 있으며 32비트 범용 레지스터인 W0~W30 레지스터도 가지고 있다.

범용 레지스터에 접근할 때 [그림 4]과 같이 X0~X30을 지정하면 64비트를 모두 사용하며 W0~W30을 지정하면 32비트만 사용한다.

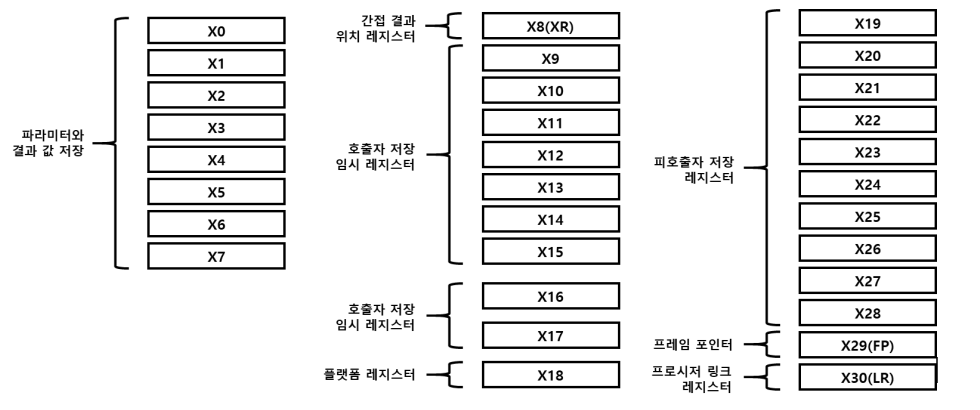

범용 레지스터는 [그림 5]와 같이 사용되는 용도가 지정되어 있다[2,7].

- X0~X7 레지스터는 Argument register로 매개변수를 함수에 전달하고 결과를 반환하는 데 사용

- AArch32의 경우 레지스터 4개를 통해 전달하였기 때문에 이를 초과하는 매개변수는 스택을 통해 전달하였으나 8개로 증가하면서 스택으로 유출할 필요성이 줄어들었다

- X8 레지스터는 특수목적 레지스터로 간접결과의 주소 위치를 전달하는 데 사용하며 X0 레지스터의 경우 함수 결과를 리턴하는 용도로 사용

- X9~X15 레지스터는 Caller-saved temporary register로 해당 레지스터값을 다른 함수 호출에서 보존해야 할 경우, 자체 스택 프레임에 저장

- X16, X17 레지스터는 Intra-procedure-call temporary register

- X19~X28 레지스터는 Callee-saved register로 호출된 함수가 복원을 담당해야 함

- X29는 프레임 포인터 레지스터(FP)로 사용

- X30은 링커 레지스터(LR)로 사용

3. ARMv8 Instruction

A. ARMv8 명령어 포맷

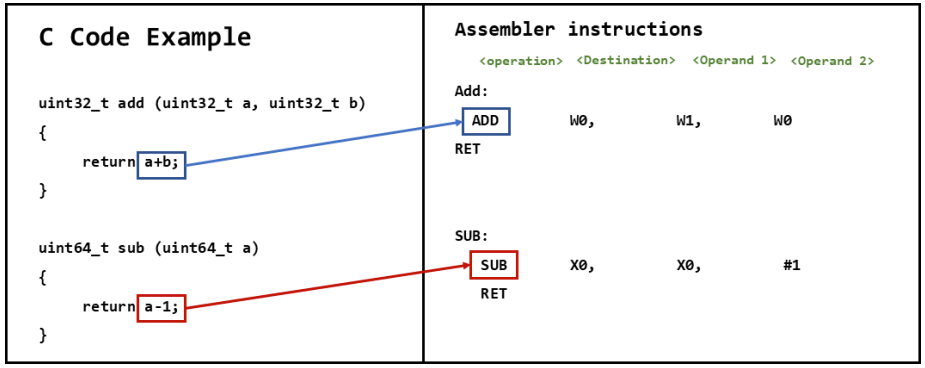

ARMv8 명령어의 포맷은 [그림 6]와 같이 Operation, Destination, Operand 1, Operand 2로 구성된다.

- Operation은 명령어 동작을 정의

- Destination은 명령어의 대상을 의미하고 항상 레지스터

- Operand 1은 명령어에 대한 첫 번째 입력값으로 항상 레지스터

- Operand 2는 두 번째 입력값으로 레지스터 또는 상수

만약 Operand 2가 레지스터일 경우에는 Shift를 포함할 수 있으며 상수일 경우에는 사용 가능한 범위가 제한되어 있다[8].

B. ARMv8 조건 필드

ARMv8에서는 조건플래그나 테스트 조건을 설정하는 몇 가지의 명령어가 존재한다. 아래 [표 3]은 조건 필드인 접미사를 정리한 내용이다[2].

C. ARMv8 주요 Instruction

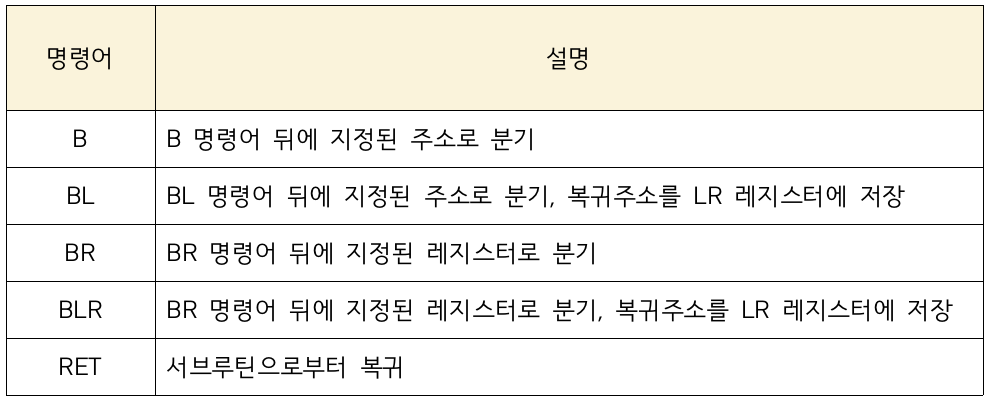

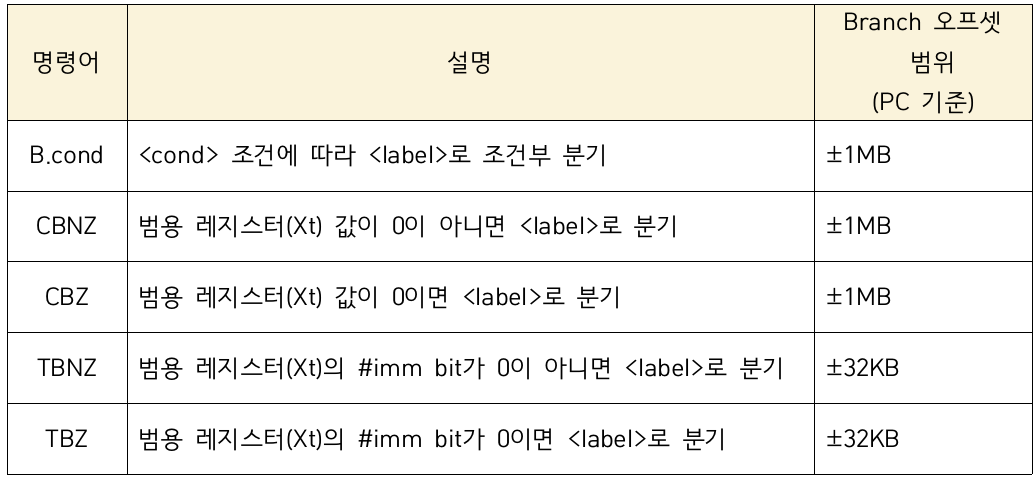

- 주요 분기 명령어

- 주요 Load / Store 명령어

- 주요 산술 및 논리 명령어

> Reference

[1] ARM Holdings, ARM-Vision, THE NEXT GENERATION OF ARM ARCHITECTURE

https://www.arm.com/campaigns/arm-vision

https://www.arm.com/campaigns/arm-vision

[2] Arm Holdings, "ARM Cortex-A Series Programmer's Guide for ARMv8-A", 2015.

[3] Apple, Apple unleashes M1

[4] Nvidia, NVIDIA Unveils NVIDIA DRIVE Atlan, an AI Data Center on Wheels for Next-Gen Autonomous Vehicles

https://nvidianews.nvidia.com/news/nvidia-unveils-nvidia-drive-atlan-an-ai-data-center-on-wheels-fornext-gen-autonomous-vehicles

https://nvidianews.nvidia.com/news/nvidia-unveils-nvidia-drive-atlan-an-ai-data-center-on-wheels-fornext-gen-autonomous-vehicles

[5] Microsoft Designing Its Own Chips for Servers, Surface PCs

[6] Arm Holdings, "ARM® Cortex® A73 Core Processor Technical Reference Manual".

[7] 윤석훈, "코드로 알아보는 ARM 리눅스 커널"

[8] Arm Holdings, "Armv8-A Instruction Set Architecture", Jun. 2019.